| 亚阈值数字标准单元库设计 |

| 发布日期:: 发布时间:2024-05-16 04:50:57 来源:爱游戏彩票官网 作者:爱游戏彩票平台 点击率:22 |

|

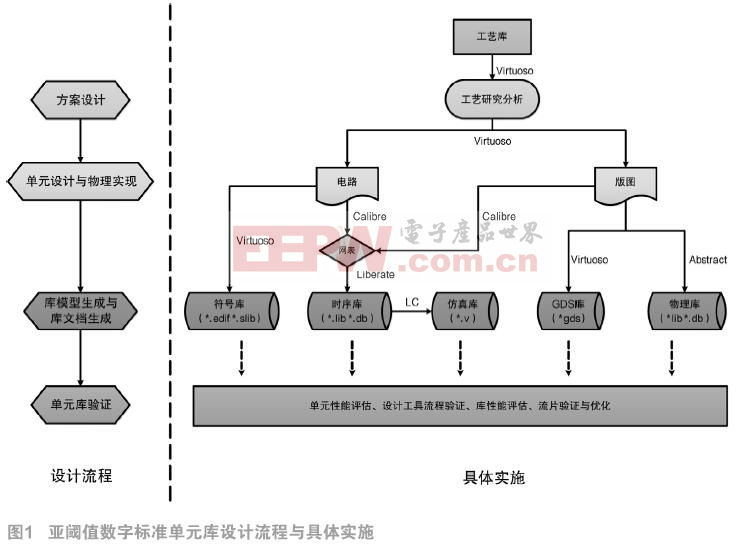

:基于对0.18 μm标准CMOS工艺的研究,本文设计了一套完备的电源电压为0.4 V的亚阈值数字标准单元库。设计流程包括工艺研究与方案设计、单元设计与物理实现、库文件的提取以及单元库验证。提出了传统沟道宽度调节与沟长偏置相结合的尺寸调整策略,有效增强PMOS管驱动并减小漏电流,提升库单元稳定性。利用ISCAS基准测试电路完成亚阈值标准单元库的验证,0.4 V电压下,相同设计,基于亚阈值数字标准单元库的设计的相比于基于商用库的设计,能耗减小20%以上,数据延时也有所减小,即亚阈值标准单元库性能明显优于商用库 作者史兴荣 何进 张九柏 张子骥 贺雅娟 电子科技大学电子科学与工程学院(成都 610054) 贺雅娟 (1978-),女,副教授,研究方向:专用集成电路与系统、超低压超低功耗数字集成电路设计等。 摘要:基于对0.18 μm标准CMOS工艺的研究,本文设计了一套完备的电源电压为0.4 V的。设计流程包括工艺研究与方案设计、单元设计与物理实现、库文件的提取以及单元库验证。提出了传统沟道宽度调节与沟长偏置相结合的尺寸调整策略,有效增强PMOS管驱动并减小漏电流,提升库单元稳定性。利用ISCAS基准测试电路完成亚阈值标准单元库的验证,0.4 V电压下,相同设计,基于的设计的相比于基于商用库的设计,能耗减小20%以上,数据延时也有所减小,即亚阈值标准单元库性能明显优于商用库相比。 随着集成电路工艺技术的不断发展,工艺线宽不断减小以追求高集成度与高速度,带来的最大问题就是功率密度的不断增大,功耗过高问题逐渐成为限制集成电路发展的重要原因。近年来兴起的无线传感网络、医疗电子和便携式消费电子等热门领域,对功耗要求越来越高,低功耗技术成为工业界和学术界研究的焦点。 在CMOS数字电路中,系统功耗包含动态功耗和静态功耗,动态功耗与供电电压的平方成正比,静态功耗与供电电压成正比,因此降低供电电压是降低功耗最有效的方法,1970年以来,极低电压设计技术的研究被广泛展开。其中亚阈值电路设计技术,通过将系统电源电压降低至器件亚阈值区域以获得极低的系统总功耗,属于系统级低功耗技术,能达到更好的降低功耗的效果,因此成为目前研究的热点。 大规模数字集成电路是基于标准单元库或者门阵列完成设计,要实现大规模亚阈值数字电路的实现,我就需要建立亚阈值数字标准单元库与亚阈值SRAM,针对亚阈值电压,对基本的逻辑门(与门、或门、非门、选择器、加法器等)以及SRAM单元进行设计和优化,使其在亚阈值下达到最优性能,进而提升整体电路性能。 本文基于0.18 μm标准工艺,首先分析了亚阈值下NMOS和PMOS失配增大的问题,并基于数字标准单元库设计流程与亚阈值单元库设计设计方法的研究,提出了传统沟道宽度调节与沟长偏置相结合的尺寸调整策略,在此基础上设计了一套电源电压为0.4 V的定制化亚阈值数字标准单元库,基于该亚阈值数字标准单元库完成数字集成电路的设计,并以ISCAS基准测试电路为载体对该亚阈值库与原商用库在0.4 V电压下重新特征化的单元库进行了对比,验证了该亚阈值数字标准单元库的完备性与功能正确性,并且在功耗和性能方面相比原商用库有很大改善。 数字标准单元库的设计就是基于Foundry提供的工艺库,定制完成基本逻辑单元的电路和版图设计,并提取相应的时序和物理信息形成文件,供综合工具和物理实现工具调用以完成数字集成电路的设计和分析。设计流程包括工艺研究分析、单元电路和版图设计、单元库建模和库文档生成、和单元库评估验证。

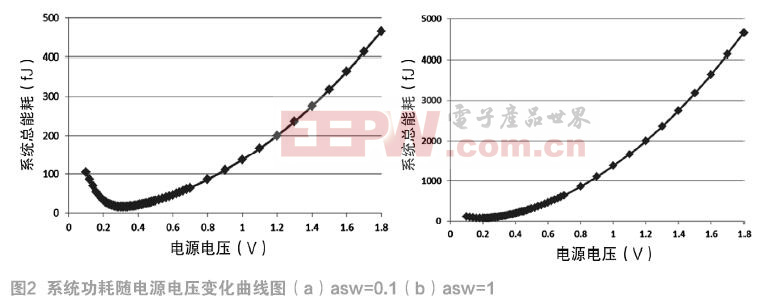

图1所示是本次亚阈值数字标准单元库设计的流程及具体实施示意图,在电路设计前,首先了解和研究该工艺的基本特性,包括晶体管电流电压特性、器件的漏极电流等参数随沟道长度和沟道宽度的变化情况,以及PMOS和NMOS的驱动强弱等,这些基于Virtuoso完成。其次,基于Virtuoso平台完成工艺研究分析以及电路图版图的设计,并基于Calibre完成单元电路网表的提取。然后,利用Liberate基于单元网表完成时序库建模,基于版图用Abstract完成物理库建模,用Library Compiler完成仿真库文件的生成,以及符号库、时序库和物理库文件的格式转换。最后,用综合和布局布线工具实现基准电路的设计,完成亚阈值库的验证工作。 亚阈值电路的理论基础就是最小能量点理论,电路总能耗包含动态能耗和动态能耗,动态能耗随着供电电压的减小呈平方关系减小,静态能耗与时钟周期、漏电流和供电电压成正比,随着电源电压的减小,尤其是在器件阈值电压下,时钟周期呈指数上升,导致漏电能耗迅速增大。由此,对于特定工艺下的电路,随着电源电压的减小,动态能耗不断减小,而静态能耗先增大,存在某一特定电源电压值,使得总能耗最小,即最小能量点,且最小能量点对应的电源电压一般在亚阈区。 为验证最小能量点理论及确定亚阈值标准单元库的电源电压,针对所涉及的工艺,设计了验证电路。验证电路包含10条50级的反相器链,通过给定10条链路不同的输入来控制开关活动性的大小,大小可以设定为0.1、0.2、……、1.0。如图2所示,分别是开关活动因子asw等于0.1和1时不同电压下的系统总功耗随电源电压变化曲线,可以看出,最小能耗点分布在电源电压为0.2 V~0.4 V范围内。本设计中,考虑到系统稳定性及数字单元库的适用范围,电源电压设定为0.4 V。

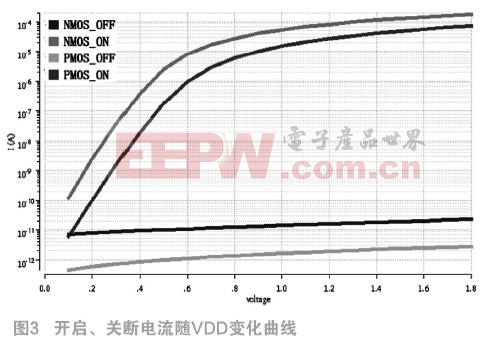

NMOS和PMOS的驱动能力是不一样的,即存在不匹配,在标准电压下(即超阈值电压),NMOS的驱动能力约为PMOS驱动能力的两倍,这得益于电子迁移率为空穴迁移率两倍多,在建立标准单元库时,单元设计时就要考虑到NMOS/PMOS失配,通过尺寸调节来实现单元的上拉下拉匹配。但是在亚阈值电压下,由MOS模型分析可知,NMOS/PMOS失配会增大,因此将商用标准单元库运用到低压电路中,电路性能会严重下降,会出现噪声容限下降,抗工艺波动能力下降,甚至逻辑误判导致电路无法正常工作等。 对相同尺寸的NMOS管和PMOS管进行仿真,晶体管的开启电流和关断电流随电源电压的变化曲线所示,随着电源电压的不断减小,NMOS管和PMOS管的开启电流和关断电流都不断减小,但是NMOS与PMOS的开启电流之比却在不断增大,在电压为0.4 V时,大尺寸管PMOS/NMOS开启电流比已接近于7,而对于最小尺寸管,甚至高达20,即PMOS和NMOS存在严重的不匹配,这给我们标准单元设计时上拉下拉平衡造成很大困难。

随着工艺尺寸的不断减小,亚阈值电压下,晶体管电流表现出明显的反短沟道效应,随着沟道长度L的变化,晶体管的开启电流表现出先增大后减小的变化趋势,即存在最优沟道长度。针对本工艺,通过对NMOS管和PMOS管的仿真发现,NMOS管开启电流不存在反短沟道效应,而PMOS管开启电流存在明显的反短沟道效应,即开启电流I_on随着沟道长度LP的增大先增大后减小,如图4所示,可以看出NMOS管开启电流在LP=200 nm时达到最大。进一步研究发现,最优沟道长度与沟道宽度相关,且增大LP存在面积和漏电流增大的不良影响,因此在实际库单元设计时,我们将NMOS的沟道长度取值为180 nm,即最小沟道长度,PMOS的沟道长度取值为190 nm,即沟道增量约为最小沟道长度的5%。

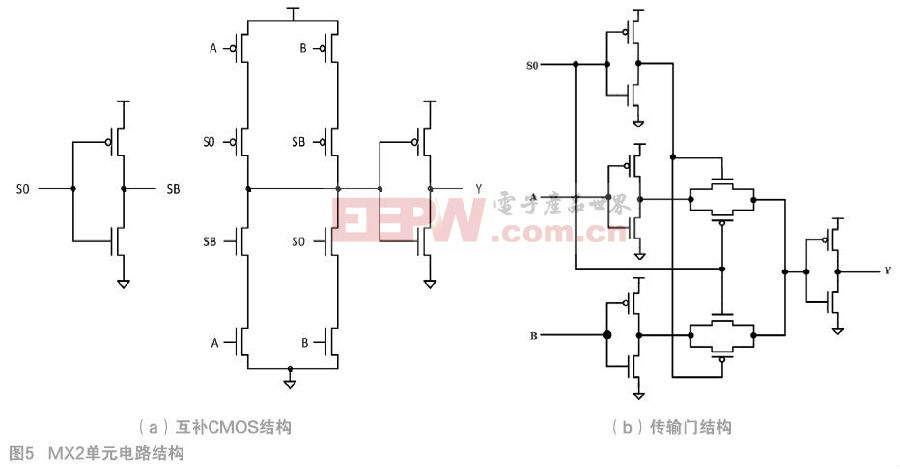

标准单元库设计中,库单元的和数量影响着综合工具在映射和优化过程的有效应,库单元种类越丰富,电路的优化就越充分。对于亚阈值标准单元库,由于电源电压较低,有些复杂单元不能工作,有些单元能工作但是稳定性大幅度下降,为保证功能正常且具有足够的稳定性,则需要对这些单元进行选择。选用扇入比较小的逻辑单元,剔除NAND4、NOR4等扇入大的逻辑,而时序优化单元较复杂且功耗较大也需要剔除,触发器和锁存器必不可少,但是其种类可以简化,时钟树逻辑单元和物理实现单元必不可少。每种逻辑又包含多种不同驱动能力,也设计了低功耗单元,对于OR2、NOR2等稳定性差的单元,为保证单元稳定性没有设计低功耗单元。 对于INV、NAND2、NOR2等简单的库单元,直接采用传统的静态互补CMOS结构,而对于MX、XOR、XNOR、DFF和LATCH等比较复杂单元,传统互补CMOS结构在亚阈值电压下稳定性不足。因此需要改变结构,采用在低压下性能更好的传输门结构设计。以二选一选择单元MX2为例说明传输门结构的优势,图5所示是MX2单元电路结构(a)互补CMOS结构(b)传输门结构。在互补CMOS结构中,有两个PMOS串联的结构,PMOS在低压下驱动很小,相同晶体管尺寸会导致单元稳定性较差,且单元延时较大。传输门结构MX2单元由传输门和反相器构成,没有PMOS串联或NMOS串联结构,能够工作在较低电压,稳定性更高。传输门速度由NMOS管决定,延时更小,且可以采用最小尺寸晶体管完成设计,功耗小。

标准单元尺寸设计,就是希望找到最优的尺寸组合,以使电路在功能正确的前提下,实现延时、功耗和面积的兼顾。基于前面第三章对工艺的分析可知,本工艺库PMOS管存在明显的电流反短沟道效应,即随着栅极长度L的增大电流先更大后减小,存在最优L值,所以采用传统栅极宽度W调节策略与栅极长度L偏置相结合的尺寸调节策略: (1)针对PMOS存在电流反短沟道效应,进一步仿真发现最优L值与晶体管栅极宽度W相关,但变化比较小,因此为简化单元仿真量,PMOS管的栅极长度统一设定为190 nm,NMOS管的栅极长度统一设定为180 nm。 (2)根据0.4V电压下的NMOS/PMOS驱动比,和具体单元的结构分析,以上拉网络和下拉网络的匹配为目标,确定PMOS和NMOS的栅极宽度W的大致范围。 (3)通过分析单元的功耗、延时和面积等参数,确定单元的优化目标函数为f(P, D)=Pi*D,P是单元功耗,由于功耗与面积正相关,也包含了对面积的考虑,D为单元延时,延时为上升下降延时的平均值,考虑了上拉网络和下拉网络的平衡以及单元稳定性。i为调节系数,用于调节单元功耗和单元延时的比重,此处i取值为1。调整单元中各晶体管栅极宽度W,使得目标函数达到最优,确定出单元的最优尺寸。

静态噪声容限是衡量单元稳定性的重要参数,测量不同逻辑单元的静态噪声容限,来评估我们设计的亚阈值库的单元稳定性。图6所示是不同逻辑单元的静态噪声容限,可以看出由于其PMOS管串联的结构特性,库中NOR2单元的静态噪声容限最小,为142 mV,占电源电压的35.5%,证明我们的库单元可以工作在很低电压。 爱游戏备用网址 |

| [←返回] |

|

上一篇:大模型“造车”新模式加速涌现 下一篇:核心工业软件:智能制造的中国“无人区” |